# 示波器如何进行 I<sup>2</sup>C、SPI、MDIO 时序分析

### 何为时序分析?

简单来说,时序(timing)就是通信总线各信号有效的先后顺序及配合关系,因而为了确保产品的稳定,需要对器件的总线通信时序进行一致性测试。

### 总线信号通信举例

#### 1. I2C

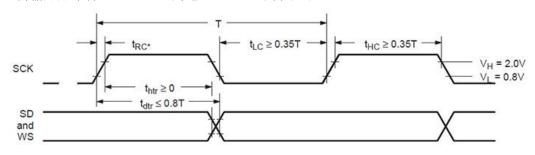

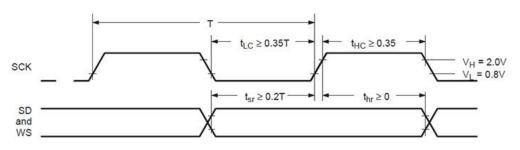

I2C 总线只需要两条线,一条 SDA 数据线,一条 SCL 时钟线,根据这两条线的高低电平、上升沿、下降沿就可以实现主机与 I2C 设备的通讯,其中有:

传输开始条件: SCL 处于高电平, SDA 下降沿时;

图 1 I2C 时序图

传输接收条件: SCL 处于高电平, SDA 上升沿时;

图 2 I2C 时序图

传输数据:开始传输后,SCL处于高电平时,SDA的数据为所传输的数据;

回应: 当传输完一个字节后,I2C 设备需要回应一个 ACK,这样主机才继续发送;因此回应信号是在传输完 8bit 后的下一个数据位(SDA 值),当 SDA 为 0 表示有回应,为 1 表示没回应。

## 2. SPI

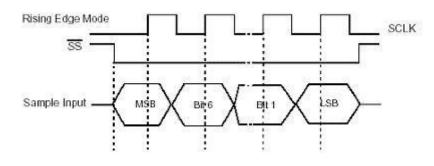

SPI 总线有四种工作方式:

- {POL,PHA}={0,0}: 时钟空闲时为低电平,上升沿采样;

- {POL.PHA}={0,1}: 时钟空闲时为低电平,下降沿采样;

- {POL,PHA}={1,0}: 时钟空闲时为高电平,下降沿采样;

- {POL,PHA}={1,1}: 时钟空闲时为高电平,上升沿采样。

图 3 SPI 时序

SPI 接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为 8 位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。在 SCLK 的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

#### 3. MDIO

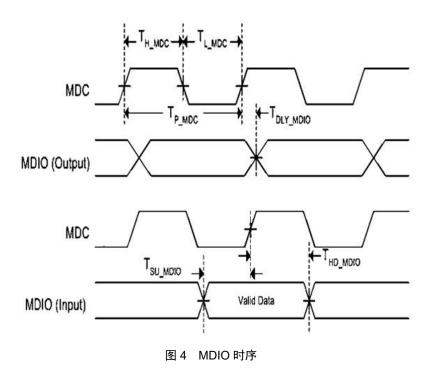

MDIO 接口(Management Data Input/Output Interface),最早在 IEEE 802.3 的第 22 卷 定义,后来在第 45 卷又定义了增强版本的 MDIO,其主要被应用于以太网的 MAC 和 PHY 层之间,用于 MAC 层器件通过读写寄存器来实现对 PHY 层器件的操作与管理。

MDIO 接口包括两条线, MDIO 和 MDC, 其中 MDIO 是双向数据线, 而 MDC 是由 STA 驱动的时钟线。MDIO 接口只是会在 MDC 时钟的上升沿进行采样, 而并不在意 MDC 时钟的频率(类似于 I2C 接口)。当 MDIO 由 STA 输出时, 需要满足建立时间、保持时间均大于 10ns。当 MDIO 由 PHY 输出时,需要满足输出延迟不超过 300ns。

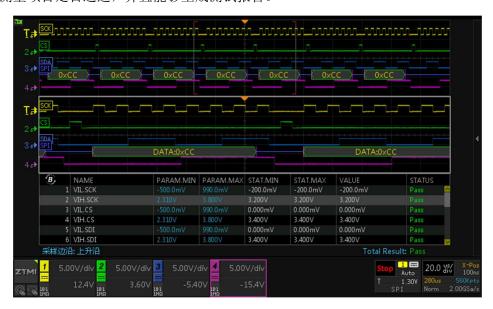

ZDS5054Pro 示波器最多支持四十多种通信协议解码,拥有 512Mpts 的存储深度,可以一次解码长时间通信报文,同时可自动分析 MDIO、I2C、SPI、CAN 等协议的通信时序。以 SPI 为例,ZDS5054Pro 系列可以对 SPI 的信号进行解码,还可以设定以下时序参数的阈值,看每一帧信号是否符合时序要求。

图 5 测试项目

整个解析到出结果的过程不超过 30 秒,在进行测试后,位于 STATUS 一栏,则会显示各项测量项目是否通过,并且能够生成测试报告。

图 6 时序测试结果